Journal of Universal Computer Science, vol. 28, no. 10 (2022), 1030-1057 submitted: 8/5/2022, accepted: 30/8/2022, appeared: 28/10/2022 CC BY-ND 4.0

# FPGA Implementation of Fast Binary Multiplication Based on Customized Basic Cells

# Abd Al-Rahman Al-Nounou

(Department of Computer Engineering, Jordan University of Science and Technology, Irbid, Jordan https://orcid.org/0000-0003-2213-9540, Amalnounou15@cit.just.edu.jo)

# **Osama Al-Khaleel**

(Department of Computer Engineering, Jordan University of Science and Technology, Irbid, Jordan https://orcid.org/0000-0003-0585-2619, oda@just.edu.jo)

# Fadi Obeidat

(Cadence Design Systems, Austin, Texas, USA https://orcid.org/0000-0002-8731-0989, fobeidat@cadence.com)

#### Mohammad Al-Khaleel

(Department of Mathematics, Khalifa University, Abu Dhabi, UAE Department of Mathematics, Yarmouk University, Irbid, Jordan

https://orcid.org/0000-0001-6266-373X, mohammad.alkhaleel@ku.ac.ae)

Abstract: Multiplication is considered one of the most time-consuming and a key operation in wide variety of embedded applications. Speeding up this operation has a significant impact on the overall performance of these applications. A vast number of multiplication approaches are found in the literature where the goal is always to achieve a higher performance. One of these approaches relies on using smaller multiplier blocks which are built based on direct Boolean algebra equations to build large multipliers. In this work, we present a methodology for designing binary multipliers where different sizes customized partial products generation (CPPG) cells are designed and used as smaller building blocks. The sizes of the designed CPPG cells are  $2 \times 2$ ,  $3 \times 3$ ,  $4 \times 4$ ,  $5 \times 5$ , and  $6 \times 6$ . We use these cells to build  $8 \times 8$ ,  $16 \times 16$ ,  $32 \times 32$ ,  $64 \times 64$ , and  $128 \times 128$  binary multipliers. All of the CPPG cells and the binary multipliers are described using the VHDL language, tested, and implemented using XILINX ISE 14.6 tools targeting different FPGA families. The implementation results show that the best performance is achieved when cell  $3 \times 3$  is used and Virtex-7 FPGA is targeted. The binary multipliers that are designed using the proposed CPPG cells achieve better performance when compared with the binary multipliers presented in the literature. As an application that utilizes the proposed multiplier, a Multiply-Accumulate (MAC) unit is designed and implemented in Spartan-3E. The implementation results of the MAC unit demonstrate the effectiveness of the proposed multiplier.

**Keywords:** Binary multiplier, Parallel Multiplier, Customized Cells, FPGA, VHDL **Categories:** B.2.4, B.6.0 **DOI:** 10.3897/jucs.86282

### **1** Introduction

Binary multipliers play a significant role in microprocessor systems [Karthikevan and Jagadeeswari, 2021][Kamrani and Heikalabad, 2021][Balasubramanian et al., 2021]. They are considered one of the critical components when it comes to performance in various kinds of Embedded Components, Digital Signals Processors, and Logical Units that execute different applications such as image processing, arithmetic, and filtering. Therefore, several research studies have been done to enhance the multiplication operation in order to improve the speed, the power consumption [Khaleqi Qaleh Jooq et al., 2021][Mounica et al., 2021], as well as the area [Sakthimohan and Deny, 2021]. Likewise, the pace of modern equipment has been increased, so the demand for highperformance systems has been rocketed [Seferlis et al., 2021]. As a result, any FP-GAs vendors provide special Logic Cores for adders and multipliers. They use memory blocks and carry chains to enhance the performance of the multiplication operation [Véstias, 2021]. The multiplier blocks which are embedded in the FPGA families are fixed in the size. Therefore, bigger multipliers are built using a different number of these blocks as shown in [Langhammer and Pasca, 2021, Singh et al., 2021]. There are three main steps to perform the conventional multiplication operation as presented in [Mao et al., 2021][Hasan and Kort, 2007]. These steps are the partial products generation, the partial products reduction, and finally, the partial products summation to obtain the final product. For example, the authors in [BN and HG, 2021] show that the basic array multiplier for two N-bit binary numbers is designed such that each bit in the multiplicand is multiplied by each bit in the multiplier to generate  $N^2$  1-bit wide partial products. This requires  $N^2$  AND gates. Full adders are then used in a two-dimensional structure to add the partial products. However, fewer and larger size partial products can be obtained by processing more than one bit from the multiplicand and the multiplier at a time. For instance, processing two bits from the multiplicand and the multiplier results in having  $\frac{N^2}{4}$  4-bit wide partial products. Similarly, the resulting partial products are to be added to generate the final product. However, larger adders are needed as the partial products are wider in this case.

Generally, binary multipliers are categorized into two main categories: parallel and serial (iterative) multipliers. In both cases, the optimization of the partial products generation and the summation of the partial products have a big impact on the performance of the multiplier [Rafiee et al., 2021]. Partial products can be generated serially or in parallel by using AND gates at the bit level or by using customized partial products generation (CPPG) cells at higher levels. The partial products summation phase is directly related to the way how they are generated. The array and tree addition schemes are used for the parallel generation case. While serial addition or accumulation fits with the serial generation case.

Much larger hardware is required in the parallel multipliers in order to reduce the multiplication latency. To generate the 1-bit wide or the n-bit wide partial products concurrently in the parallel multipliers, many AND gates or CPPG cells are required. In this case, a parallel addition structure, that uses many adders, can be used to obtain the final product [Christilda and Milton, 2021][Lee and Burgess, 2003][Beuchat and Tisserand, 2002] in a shorter time compared to the iterative multipliers.

This work designs high-speed and low-area binary multipliers to be used in any application where the multiplication operations have a big impact on the overall performance of the application. Different size customized partial products generation (CPPG) cells are proposed to be used as building blocks in the binary multipliers. These CPPG

cells are designed following the traditional logic design and Boolean algebra. The impact of these cells on the performance is studied by using them in designing different size binary multipliers and testing their performance.

Our proposed multipliers are exact multipliers that produce exact results. They are not approximate multipliers. Approximate multipliers are smaller and faster than exact multipliers. However, they produce inexact results. Therefore, they are suitable for only applications that do not require exact results. If the approximate multiplier gives results far away from the exact ones, an application that uses this multiplier will not give the expected output. Thus, the efficiency of an approximate multiplier that is being used in an application must be verified such that the application still works properly and correctly. This is not the case with the exact multipliers, which can be used in any application, and the expected output of the application is still achieved.

The rest of this paper is organized as follows: Section 2 provides a summary of some related works in the literature. Section 3 provides a detailed explanation of the design methodology of the CPPG cells and how they are used to design binary multipliers. The experimental results and the comparisons are presented and discussed in Section 4. Finally, the conclusions are provided in Section 5.

# 2 Background and literature review

Many research studies in the literature address the binary multiplication operation and its implementation. Some of these studies focus on improving the multiplication process by the enhancement of the partial products generation only. On the other hand, there are several research studies that improve the multiplication process by enhancing the partial products generation and the partial products summation.

In [Asati and Chandrashekhar, 2009], the authors explore a new structure for multiplying two binary numbers using a hierarchical design approach. They design a  $(16 \times 16)$  unsigned multiplier which is considered an array of array multiplier that has better performance than the array multiplier. This category of the multiplier is built based on smaller multiplication cells. A  $(2 \times 2)$  multiplication cell is designed using the traditional combinational logic circuit design approach where truth table and Karnaugh map are used to generate optimized Boolean equations that model the design. The  $(2 \times 2)$  multiplication cell is used to design an  $(8 \times 8)$  multiplication cell. Finally, the  $(8 \times 8)$  multiplication cell is used to design a  $(16 \times 16)$  binary multiplier. The design is implemented using CMOS technology and is compared with the 16-bit Booth encoded Wallace tree multiplier, which is implemented in [Fadavi-Ardekani, 1993]. The design shows an improvement in terms of latency and power consumption with a doubled number of transistors. However, they do not investigate arbitrary or bigger multipliers other than the  $(16 \times 16)$  multiplier.

The authors in [Das and Rahaman, 2010], pursue the same technique that is followed in [Asati and Chandrashekhar, 2009]. They use the  $2 \times 2$  multiplier cell to design signed numbers binary multiplier. The partial products are added using parallel addition and the design is compared with the Baugh Wooley multiplier which is implemented in [Baugh and Wooley, 1973]. The proposed methodology provides better performance with larger area and higher power dissipation. Also, their proposed design expends more power rather than the Baugh Wooley multiplier. Similarly, they do not generalize their method for larger multipliers. Only  $16 \times 16$  multiplier is investigated as in [Asati and Chandrashekhar, 2009]. A 128×128 multiplier is proposed in [Nagaraju and Reddy, 2014]. The authors invest the technique of ancient mathematics to implement and enhance their multiplier. They design the  $128 \times 128$  multiplier by using  $64 \times 64$  multiplier blocks, which are built from 3.96  $ns 4 \times 4$  Vedic multiplier blocks. Better performance is achieved in comparison to the conventional multipliers.

An energy-efficient radix-16 Booth multiplier is proposed in [Mounica et al., 2021]. The design is used for both signed and unsigned numbers. The delay and energy are improved by optimizing the partial product generation unit. Two architectures of the multiplier are presented. One is non-pipelined and the other is pipelined. The signed, unsigned and combined (signed/unsigned) versions of the multiplier are investigated.

A sequential  $8 \times 8$  multiplier is presented in [Hameed and Kathem, 2021]. An iterative addition approach is defined such that the number of iterative additions, required to generate the final product, is reduced. All of the intermediate shift operations, required in the conventional serial multiplication, are replaced by only one shift operation applied to the final result. Both of the proposed and conventional multipliers are implemented and compared in terms of time delay.

The work in [Fonseca et al., 2005] puts more effort to enhance the performance of binary multiplication using carry-save addition array structure presented in [Kim et al., 1998]. On the other hand, the authors use a type of  $2 \times 2$  cell to generate the partial products and they build a hybrid multiplier. Their approach is based on the 2's complement encoding. Signed and unsigned operands are investigated. The authors compare their results with the modified Booth multiplier in terms of power, area, and delay. They use the Altera Quartus II and target the Altera Stratix FPGA family. The power consumption is reduced by 25% with area and delay penalty.

A radix-4 multiplexer-based array binary multiplier is presented in [Al-Khaleel et al., 2006]. The multiplier is used in designing a scalable and large moduli multiplier for public-key cryptographic systems. The authors target Virtex-4 FPGA family. To fit up to 512-bit modular multiplications on a single FPGA device, the authors use a novel partitioning and pipeline folding scheme.

A new architecture for the 8-bit Radix-4 modified Booth multiplier is presented in [Rafiq et al., 2021]. The proposed multiplier runs at a frequency of 500 MHz with low power and delay. A new encoder is used to reduce the first partial product array circuitry. The proposed multiplier is synthesized using Cadence Virtuoso and 90nm process technology.

The authors in [Singh and Singh, 2016a] utilize the work in [Singh and Singh, 2016b] to implement a  $16 \times 16$  Vedic multiplier based on investing the architecture of the Brent Kung adder. The authors design a  $2 \times 2$  Vedic multiplier and use it to build a  $4 \times 4$  Vedic multiplier. Then, they used the  $4 \times 4$  Vedic multiplier to design an  $8 \times 8$  Vedic multiplier. Finally, they use four blocks of the  $8 \times 8$  Vedic multiplier to design their  $16 \times 16$  Vedic multiplier. They compare their work with Vedic multiplier using MUX-based adder.

A (64-bit) Vedic multiplier is presented in [Karthik et al., 2021]. The authors use half adders for adding the partial products. They achieve better performance in area and delay in comparison with the Array and Booth multipliers.

The authors in [Atre and Alshewimy, 2017] utilize both Wallace Tree and Modified Booth's Algorithm structure for designing different size multipliers. The sizes of the operands are 8-bit, 16-bit, 32-bit, 64-bit, and 128-bit. Wallace Tree decreases the number of sequential summation steps to achieve better speed. They achieve an improvement in the time delay with some area penalty.

A technique of building a larger multiplier from smaller blocks is used in [Jais and Palsodkar, 2016]. A 64-bit Vedic multiplier is designed starting based on a 2-bit Vedic

multiplier. The authors target three different FPGA families: Spartan-6, Virtex-5, and Virtex-6. Verilog HDL is used to describe the designs and the results are compared with three familiar multipliers: Karatsuba, Vedic-Karatsuba, and Optimized Vedic multiplier.

Parallel computation of the partial products is investigated in [Naqvi, 2017] to design a 64-bit Vedic multiplier. The Carry-save adder and concatenation technique are used to enhance the performance of this multiplier. Three different FPGA devices (Spartan-3, Virtex-5, and Virtex-6) are targeted and a comparison between the proposed multiplier and four related works is made.

A carry-save adder is used instead of a parallel adder to design a modified Vedic multiplier for binary numbers in [Akhter and Chaturvedi, 2019]. The authors use four  $(8 \times 8$ -bit) Vedic multiplier blocks and 16-bit carry-save addition to build their  $16 \times 16$  bit modified multiplier.

An 8-bit Vedic multiplier by using Urdhva Tiryaghyam sutra is proposed in [Chandrashekara and Rohith, 2019]. A modified carry-save adder is used in the addition phase. The work is compared against the array, the Wallace Tree, and the Booth multipliers. The proposed design shows better area and delay results compared with similar works in literature.

An approximate multiplier, which is efficiently deployed on FPGAs, is presented in [Van Toan and Lee, 2020]. The main goal is to achieve low power, small area, and high speed; while maintaining acceptable accuracy such that an application that utilizes the multiplier still gives proper output. An image processing application is used to verify the effectiveness and applicability of the multiplier.

The authors of [Moss et al., 2019] present a two-speed, radix-4, serial-parallel multiplier. The latency of their design depends on the multiplier value. This is because their multiplier is basically a modified radix-4 Booth multiplier that adds only the nonzero Booth encodings and skips over the zero operations. VerilogHDL and Intel Cyclone-V FPGA are used to implement the proposed multiplier. The implementation results, depending on the input set, show better performance over the standard parallel Booth multiplier in terms of area-time.

After a careful study of the related work presented in the literature, one can conclude that some works design a  $2 \times 2$  multiplication cell using the traditional logic design and Boolean algebra. The  $2 \times 2$  cell is used in these works to generate the partial products in a binary multiplier. Some works use such cell to design larger cells like  $4 \times 4$  and  $8 \times 8$  and then use them to design larger multipliers. However, up to the knowledge of the authors, no work in literature builds cells larger than  $2 \times 2$  using the traditional logic design and Boolean algebra and uses them in designing large binary multipliers. Especially, when it comes to larger bit-width multipliers such as the  $128 \times 128$  multiplier. Therefore, in this work, different sizes of customized partial products generation (CPPG) cells are designed using the traditional logic design and Boolean algebra. The CPPG cells are then used in designing  $8 \times 8$ ,  $16 \times 16$ ,  $32 \times 32$ ,  $64 \times 64$ , and  $128 \times 128$  binary multipliers. VHDL description for each CPPG cell and for each multiplier is developed. The VHDL is portable and can be implemented in any FPGA or ASIC platform. However, since we only have access to Xilinx platform, our implementations are done in Xilinx FPGAs using Xilinx CAD tools.

# 3 The proposed binary multipliers

In the proposed methodology, five customized partial products generation cells (CPPG) are designed using the traditional digital logic design approach, which is used in [Al-

Khaleel et al., 2011a], [Al-Khaleel et al., 2011b], [Al-Khaleel et al., 2013], and [Al-Khaleel et al., 2015] to obtain optimized Boolean equations. The optimization guarantees a minimal number of product terms and a minimal number of literals within each term. The number of the product terms affects the number of the AND gates, the number of the OR gates, and the size of the OR gates. While the number of literals within each term affects the size of the AND gates. The sizes of the proposed CPPG cells are  $2 \times 2, 3 \times 3, 4 \times 4, 5 \times 5$ , and  $6 \times 6$ . A  $r \times r$  CPPG cell is used to multiply r bits from the multiplier by r bits from the multiplicand to generate one partial product of 2r bits. Multiple instances of each cell are used to concurrently generate the partial products in the binary multiplier. The generated partial products are then added to generate the final product. The cells are used to design binary multipliers with different operand sizes.

#### Using the 2×2 CPPG cell to design $n \times m$ Multiplier 3.1

The optimized Boolean functions for the  $2 \times 2$  CPPG cell are given in Equation 1. This cell multiplies the 2-bit numbers  $(a_1a_0 \text{ and } b_1b_0)$  and produces the 4-bit partial product  $c_3 c_2 c_1 c_0$ .

$$c_{3} = a_{1}a_{0}b_{1}b_{0},$$

$$c_{2} = a_{1}b_{1}\bar{b_{0}} \lor a_{1}\bar{a_{0}}b_{1}b_{0},$$

$$c_{1} = \bar{a_{1}}a_{0}b_{1} \lor a_{1}\bar{b_{1}}b_{0} \lor a_{1}\bar{a_{0}}b_{1}b_{0} \lor a_{0}b_{1}\bar{b_{0}},$$

$$c_{0} = a_{0}b_{0}.$$

(1)

To generalize the approach for any multiplier size, the sizes of the operands of the multiplier A and B are considered to be n-bit and m-bit, respectively. Both n and m must be multiple of 2 integers in this case. If this condition is not valid, then zeros can be padded to the left of the number such that the sizes of the operands are multiple of 2. A can be represented as shown by Equation 2.

$$A = (A_{n-1}A_{n-2}A_{n-3}A_{n-4}\dots A_3A_2A_1A_0)_2.$$

(2)

Furthermore, A can be decomposed as given in Equation 3.

$$A = (A_{n-1}A_{n-2} \underbrace{00...00}_{(n-2)zeros})_2 + (00A_{n-3}A_{n-4} \underbrace{00...00}_{(n-4)zeros})_2 + \cdots + (\underbrace{00...00}_{(n-4)zeros} A_3A_200)_2 + (\underbrace{00...00}_{(n-2)zeros} A_1A_0)_2.$$

(3)

Replace the k zeros on the right side of each term with  $2^k$  to get Equation 4.

$$A = 2^{n-2} (A_{n-1}A_{n-2})_2 + 2^{n-4} (A_{n-3}A_{n-4})_2 + \dots + 2^2 (A_3A_2)_2 + 2^0 (A_1A_0)_2.$$

(4)

Let  $X_{\frac{k}{2}} = (A_{k+1}A_k)_2$ ;  $k = 0, 2, 4, \dots, n-2$ . Then A can be expressed as in Equation 5.

$$A = 2^{n-2} X_{\frac{n}{2}-1} + 2^{n-4} X_{\frac{n}{2}-2} + \dots + 2^2 X_1 + 2^0 X_0 = \sum_{i=0}^{\frac{n}{2}-1} 2^{2i} X_i.$$

(5)

1036 Al-Nounou A.A., Al-Khaleel O., Obeidat F., Al-Khaleel M.: FPGA Implementation ...

Similarly, *B* can be represented and decomposed as given by Equations 6 and 7, respectively.

$$B = (B_{m-1}B_{m-2}B_{m-3}B_{m-4}\dots B_3B_2B_1B_0)_2, \tag{6}$$

$$B = (B_{m-1}B_{m-2} \underbrace{00...00}_{(m-2)zeros})_2 + (00B_{m-3}B_{m-4} \underbrace{00...00}_{(m-4)zeros})_2 + \cdots + (\underbrace{00...00}_{(m-4)zeros} B_3 B_2 0 0)_2 + (\underbrace{00...00}_{(m-2)zeros} B_1 B_0)_2.$$

(7)

Replace the k zeros on the right side of each term with  $2^k$  to get Equation 8.

$$B = 2^{m-2} (B_{m-1}B_{m-2})_2 + 2^{m-4} (B_{m-3}B_{m-4})_2 + \dots + 2^2 (B_3B_2)_2 + 2^0 (B_1B_0)_2.$$

(8)

Let  $Y_{\frac{k}{2}} = (B_{k+1}B_k)_2$ ;  $k = 0, 2, 4, \dots, m-2$ . Then B can be expressed by Equation 9.

$$B = 2^{m-2}Y_{\frac{m}{2}-1} + 2^{m-4}Y_{\frac{m}{2}-2} + \dots + 2^{2}Y_{1} + 2^{0}Y_{0} = \sum_{j=0}^{\frac{m}{2}-1} 2^{2j}Y_{j}.$$

(9)

Hence, the final product C can be obtained by Equation 10.

$$C = A \times B$$

=  $\sum_{i=0}^{\frac{n}{2}-1} 2^{2i} X_i \times \sum_{j=0}^{\frac{m}{2}-1} 2^{2j} Y_j$

=  $\sum_{i=0}^{\frac{n}{2}-1} \sum_{j=0}^{\frac{m}{2}-1} 2^{2i} X_i \times 2^{2j} Y_j = \sum_{i=0}^{\frac{n}{2}-1} \sum_{j=0}^{\frac{m}{2}-1} 2^{2(i+j)} X_i Y_j.$  (10)

$X_i Y_j$  represents the partial product number  $\frac{n}{2}i + j$ , which is represented as  $PP_{\frac{n}{2}i+j}$ . Therefore, C can be represented in terms of the partial products as in Equation 11.

$$C = \sum_{i=0}^{\frac{n}{2}-1} \sum_{j=0}^{\frac{m}{2}-1} 2^{2(i+j)} P P_{\frac{n}{2}i+j}.$$

(11)

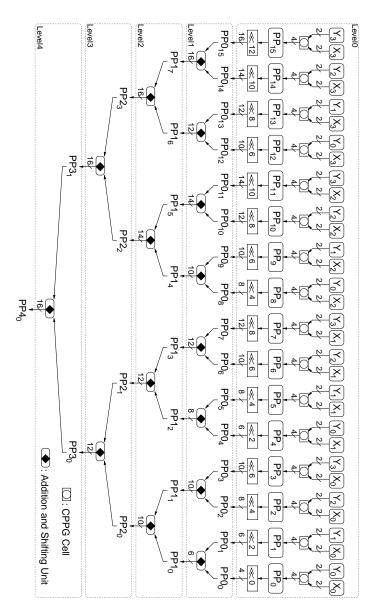

The total number of the partial products before shifting is  $\frac{n}{2} \times \frac{m}{2} = \frac{mn}{2^2}$ . These partial products are  $PP_{\frac{ni}{2}+j}$  for  $(i, j) = (0, 0), (0, 1), \dots, (0, \frac{m}{2} - 1), (1, 0), (1, 1), \dots, (\frac{n}{2} - 1, 0), (\frac{n}{2} - 1, 1), \dots, (\frac{n}{2} - 1, \frac{m}{2} - 1)$ . As illustrated in Figure 1, which presents the structure of an  $8 \times 8$  multiplier using the  $2 \times 2$  CPPG cell, each of these none shifted partial products is generated using one  $2 \times 2$  CPPG cell in *Level*0 of the structure. Therefore, the total number of the  $2 \times 2$  CPPG cells that are required to generate the none shifted partial products is  $\frac{mn}{2^2}$ . These none shifted partial products are shifted and then added in the addition stage according to Equation 11. The shifted partial products are the outputs from *Level*0 of the structure. They are obtained using Equation 12 where the superscript *l* represents the level that outputs the shifted partial products, which is in this case

# Level0 (i.e. l = 0).

$$PP_{\frac{n}{2}i+j}^{l} = 2^{2(i+j)}PP_{\frac{n}{2}i+j},$$

for  $l = 0$  and  $(i, j) = (0, 0), (0, 1), \dots, (0, \frac{m}{2} - 1), (1, 0), (1, 1), \dots, (\frac{n}{2} - 1, 0), (\frac{n}{2} - 1, 1), \dots, (\frac{n}{2} - 1, \frac{m}{2} - 1).$  (12)

*Figure 1: The structure of an*  $8 \times 8$  *multiplier using the*  $2 \times 2$  *CPPG cell.*

For the addition phase, the tree structure is adopted to enhance the speed as illustrated in Figure 1. The shifted partial products from Level0 are inputs to the first level (Level1) of the addition phase. The total number of inputs to Level1 must be powers of 2. Therefore, if the number of the shifted partial products is not powers of 2, additional partial products with 0 values must be padded with the shifted partial products to form the inputs to Level1. The number of the additional partial products D is given by Equation 13. This means that the total number of inputs to Level1 is  $\frac{mn}{2^2} + D$ . It should be pointed out that padding the 0 values additional partial products do not affect the performance or the area of the design as the design tools trim out any none used hardware. For example, if an adder is instantiated within the VHDL code and it happens that the inputs to the adder have 0 values, then the tool trims out this adder and it will not be part of the final design. The goal of having the number of the inputs to Level1 powers of 2 is to maintain a regular structure that facilitates generic VHDL coding.

$$D = 2^{\lceil (\log_2 \frac{mn}{2^2}) \rceil} - \frac{mn}{2^2}$$

(13)

All of the shifted partial products from Level0 and the additional padded partial products are added in the first level (Level1) of the addition phase such that each two consecutive partial products are added using one binary adder. That is  $PP_1^0$  is added with  $PP_0^0$ ,  $PP_0^0$  is added with  $PP_2^0$ , and so on. In general,  $PP_{2t}^0$  is added with  $PP_{2t+1}^0$  for  $t = 0, 1, 2, \ldots, (\frac{mn}{2^2} + D)/2 - 1$ . There are  $(\frac{mn}{2^2} + D)/2$  output results from Level1 of the addition phase, which are the inputs to Level2. Hence, there are  $(\frac{mn}{2^2} + D)/4$  output results from Level2 of the addition phase, which are the inputs to Level3 and so on. In general, for a given level l in the addition stage, there are  $(\frac{mn}{2^2} + D)/2^{l-1}$  inputs and  $(\frac{mn}{2^2} + D)/2^l$  outputs. This means that the number of adders in a given level l is  $(\frac{mn}{2^2} + D)/2^l$ . The outputs of a given level l in the addition phase are obtained based on equation 14.

$$PP_t^l = (PP_{(2t+1)}^{l-1} + PP_{2t}^{l-1}), \text{ for } t = 0, 1, 2, 3, \dots, (\frac{mn}{2^2} + D)/2^l - 1.$$

(14)

In the last level (l = L), there are two results to be added. Hence, for the last level, it can be stated that  $((\frac{mn}{2^2} + D)/2^{L-1} = 2)$ . It can be easily shown that solving for L, which is an integer that represents the number of the levels in the addition phase, one gets  $L = \log_2(\frac{mn}{2^2} + D)$ .

#### **3.2** Using the $3 \times 3$ CPPG cell to design $n \times m$ multiplier

The optimized Boolean functions for the  $3 \times 3$  CPPG cell are obtained in a similar way to that used for the  $2 \times 2$  CPPG cell. They are presented in Equation 15. This cell multiplies the 3-bit numbers ( $a_2a_1a_0$  and  $b_2b_1b_0$ ) and produces the 6-bit partial product  $c_5c_4c_3c_2c_1c_0$ .

$c_5 = a_2 a_1 a_0 b_2 b_0 \lor a_2 a_0 b_2 b_1 b_0 \lor a_2 a_1 b_2 b_1,$

- $\begin{aligned} c_4 &= a_2 \bar{a_1} a_0 b_2 \bar{b_1} b_0 \lor a_2 \bar{a_1} \bar{a_0} b_2 b_1 b_0 \lor \bar{a_2} a_1 a_0 b_2 b_1 \lor a_2 a_1 \bar{b_2} b_1 b_0, \\ &\lor a_2 \bar{a_0} b_2 \bar{b_1} b_0 \lor a_2 \bar{a_1} b_2 b_1 \bar{b_0} \lor a_2 a_1 a_0 b_1 b_0 \lor a_2 b_2 \bar{b_1} \bar{b_0}, \end{aligned}$

- $c_{3} = \bar{a_{2}}a_{1}a_{0}\bar{b_{2}}b_{1}b_{0} \lor a_{2}\bar{a_{1}}a_{0}b_{2}\bar{b_{1}}b_{0} \lor \bar{a_{2}}a_{1}b_{2}\bar{b_{1}} \lor a_{2}\bar{a_{1}}\bar{a_{0}}b_{2}b_{1}b_{0} \lor a_{2}\bar{a_{1}}b_{2}b_{1}\bar{b_{0}},$  $\lor a_{2}\bar{a_{1}}\bar{b_{2}}b_{1}b_{0} \lor \bar{a_{2}}a_{1}\bar{a_{0}}b_{2} \lor a_{2}\bar{b_{2}}b_{1}\bar{b_{0}} \lor a_{1}b_{2}\bar{b_{1}}\bar{b_{0}} \lor a_{1}\bar{a_{0}}b_{2}b_{0} \lor a_{2}a_{0}b_{1}\bar{b_{0}},$ (15)

- $c_{2} = a_{2}\bar{a_{1}}\bar{a_{0}}b_{2}b_{1}b_{0} \lor a_{2}\bar{a_{0}}b_{2}\bar{b_{1}}b_{0} \lor a_{2}\bar{a_{1}}\bar{b_{2}}b_{1}b_{0} \lor \bar{a_{2}}a_{1}\bar{a_{0}}b_{1} \lor a_{2}\bar{b_{2}}\bar{b_{1}}b_{0},$  $\lor \bar{a_{1}}a_{0}b_{2}\bar{b_{0}} \lor a_{1}\bar{b_{2}}b_{1}\bar{b_{0}} \lor a_{1}\bar{a_{0}}b_{1}\bar{b_{0}} \lor a_{0}b_{2}\bar{b_{1}}\bar{b_{0}} \lor a_{2}a_{0}\bar{b_{2}}b_{0} \lor \bar{a_{2}}a_{0}b_{2}b_{0},$

$$c_1 = \bar{a_1}a_0b_1 \vee a_1\bar{a_0}b_0 \vee a_1\bar{b_1}b_0 \vee a_0b_1\bar{b_0},$$

$c_0 = a_0 b_0.$

For generality, the sizes of the operands A and B are assumed to be n-bit and m-bit, respectively. Both n and m should be multiple of 3 integers in this case. If this condition is not valid, then again, zeros are padded to the left of the number to make the size of the operands multiple of 3. A can be represented as given by Equation 16.

$$A = (A_{n-1}A_{n-2}A_{n-3}\dots A_2A_1A_0)_2.$$

(16)

Moreover, A can be decomposed as shown in Equation 17.

$$A = (A_{n-1}A_{n-2}A_{n-3}\underbrace{000\dots00}_{(n-3)zeros})_2 + (000A_{n-4}A_{n-5}A_{n-6}\underbrace{000\dots00}_{(n-6)zeros})_2 + \cdots + (\underbrace{000\dots00}_{(n-6)zeros}A_5A_4A_3000)_2 + (\underbrace{000\dots000}_{(n-3)zeros}A_2A_1A_0)_2.$$

(17)

Replacing the k zeros on the right side of each term with  $2^k$  implies Equation 18.

$$A = 2^{n-3} (A_{n-1}A_{n-2}A_{n-3})_2 + 2^{n-6} (A_{n-4}A_{n-5}A_{n-6})_2 + \dots + 2^3 (A_5A_4A_3)_2 + 2^0 (A_2A_1A_0)_2.$$

(18)

Assume  $X_{\frac{k}{3}} = (A_{k+2}A_{k+1}A_k)_2$ ;  $k = 0, 3, 6, \dots, n-3$ , then A can be expressed as in Equation 19.

$$A = 2^{n-3}X_{\frac{n}{3}-1} + 2^{n-6}X_{\frac{n}{3}-2} + \dots + 2^{3}X_{1} + 2^{0}X_{0} = \sum_{i=0}^{\frac{n}{3}-1} 2^{3i}X_{i}.$$

(19)

Similarly, B can be represented and decomposed as given by Equations 20 and 21, respectively.

$$B = (B_{m-1}B_{m-2}B_{m-3}\dots B_2B_1B_0)_2,$$

(20)

and

$$B = (B_{m-1}B_{m-2}B_{m-3}\underbrace{000\dots000}_{(m-3)zeros})_2 + (000B_{m-4}B_{m-5}B_{m-6}\underbrace{000\dots000}_{(m-6)zeros})_2 + \dots + (\underbrace{000\dots000}_{(m-6)zeros}B_5B_4B_3000)_2 + (\underbrace{000\dots000}_{(m-3)zeros}B_2B_1B_0)_2.$$

(21)

Replacing the k zeros on the right side of each term with  $2^k$  leads to Equation 22.

$$B = 2^{m-3} (B_{m-1}B_{m-2}B_{m-3})_2 + 2^{m-6} (B_{m-4}B_{m-5}B_{m-6})_2 + \dots + 2^3 (B_5B_4B_3)_2 + 2^0 (B_2B_1B_0)_2.$$

(22)

Assume  $Y_{\frac{k}{3}} = (B_{k+2}B_{k+1}B_k)_2$ ;  $k = 0, 3, 6, \dots, m-3$  then B can be expressed by Equation 23.

$$B = 2^{m-3}Y_{\frac{m}{3}-1} + 2^{m-6}Y_{\frac{m}{3}-2} + \dots + 2^{3}Y_{1} + 2^{0}Y_{0} = \sum_{j=0}^{\frac{m}{3}-1} 2^{3j}Y_{j}.$$

(23)

Hence, the final product C can be obtained by Equation 24.

$$C = A \times B = \sum_{i=0}^{\frac{n}{3}-1} 2^{3i} X_i \times \sum_{j=0}^{\frac{m}{3}-1} 2^{3j} Y_j = \sum_{i=0}^{\frac{n}{3}-1} \sum_{j=0}^{\frac{m}{3}-1} 2^{3i} X_i \times 2^{3j} Y_j$$

$$= \sum_{i=0}^{\frac{n}{3}-1} \sum_{j=0}^{\frac{m}{3}-1} 2^{3(i+j)} X_i Y_j.$$

(24)

$X_i Y_j$  represents the partial product number  $\frac{n}{3}i + j$ , which is represented as  $PP_{\frac{n}{3}i+j}$ . Therefore, C can be represented in terms of the partial products as in Equation 25.

$$C = \sum_{i=0}^{\frac{n}{3}-1} \sum_{j=0}^{\frac{m}{3}-1} 2^{3(i+j)} P P_{\frac{ni}{3}+j}.$$

(25)

In this case, the total number of the partial products before shifting is  $\frac{n}{3} \times \frac{m}{3} = \frac{mn}{3^2}$ . These partial products are:

$PP_{\frac{n}{3}i+j} \text{ for } (i,j) = (0,0), (0,1), \dots, (0,\frac{m}{3}-1), (1,0), (1,1), \dots, (\frac{n}{3}-1,0), (\frac{n}{3}-1), (1,0), (1,1), \dots, (\frac{n}{3}-1), (1,0), (1,1), \dots, (\frac{n}{3}-1), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0), (1,0),$

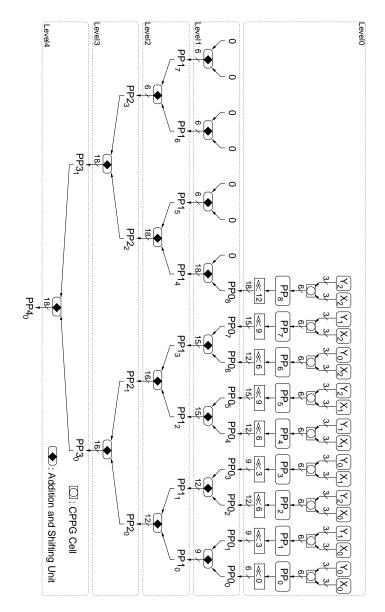

1, 1), ...,  $(\frac{n}{3} - 1, \frac{m}{3} - 1)$ . Again, the process is illustrated in Figure 2 where the structure of an 8 × 8 multiplier using the the 3×3 CPPG cell is presented. Since 8 is not multiple of 3, a 0 is padded to the left of the most significant bit of multiplier and to the left of the most significant bit of the multiplicand. As a result both n and m become 9-bit in size. Each of the none shifted partial products is generated using one 3×3 CPPG cell in Level0 of the structure. Therefore, the total number of the  $3 \times 3$  CPPG cells that are required to generate the none shifted partial products is  $\frac{mn}{3^2}$ . These none shifted partial products are shifted and then added in the addition stage according to Equation 25. The shifted partial products are

the outputs from Level0 of the structure. They are obtained using Equation 26 where the superscript l represents the level that outputs the shifted partial products, which is in this case Level0 (i.e. l = 0).

$$PP_{\frac{n}{3}i+j}^{l} = 2^{3(i+j)}PP_{\frac{n}{3}i+j},$$

for  $l = 0$  and  $(i, j) = (0, 0), (0, 1), \dots, (0, \frac{m}{3} - 1), (1, 0), (1, 1), \dots, (\frac{n}{3} - 1, 0), (\frac{n}{3} - 1, 1), \dots, (\frac{n}{3} - 1, \frac{m}{3} - 1).$  (26)

The number of the shifted partial products from Level0 is 9 which is not powers of 2. Therefore, additional partial products with 0 values must be padded with the shifted partial products to form the inputs to Level1. The number of the additional partial products D is given by Equation 27. In this case D = 7. This means that the total number of inputs to Level1 is  $\frac{mn}{3^2} + D = 16$ .

$$D = 2^{\lceil (\log_2 \frac{mn}{3^2}) \rceil} - \frac{mn}{3^2}$$

(27)

Again, all of the shifted partial products from Level0 and the additional padded partial products are added in the first level (Level1) of the addition phase such that each two consecutive partial products are added using one binary adder. That is  $PP_1^0$  is added with  $PP_0^0$ ,  $PP_3^0$  is added with  $PP_2^0$ , and so on. In general,  $PP_{2t}^0$  is added with  $PP_{2t+1}^0$  for  $t = 0, 1, 2, \ldots, (\frac{mn}{32} + D)/2 - 1$ . There are  $(\frac{mn}{32} + D)/2$  output results from Level1 of the addition phase, which are the inputs to Level2. Hence, there are  $(\frac{mn}{32} + D)/4$  output results from Level2 of the addition phase, which are the inputs to Level3 and so on. In general, for a given level l in the addition stage, there are  $(\frac{mn}{32} + D)/2^{l-1}$  inputs and  $(\frac{mn}{32} + D)/2^l$  outputs. This means that the number of adders in a given level l is  $(\frac{mn}{32} + D)/2^l$ . The outputs of a given level l in the addition phase are obtained based on equation 28.

$$PP_t^l = (PP_{(2t+1)}^{l-1} + PP_{2t}^{l-1}), \text{ for } t = 0, 1, 2, 3, \dots, (\frac{mn}{3^2} + D)/2^l - 1.$$

(28)

In the last level (l = L), there are two results to be added. Hence, for the last level, it can be stated that  $((\frac{mn}{3^2} + D)/2^{L-1} = 2)$ . It can be easily shown that solving for L, which is an integer that represents the number of the levels in the addition phase, one gets  $L = \log_2(\frac{mn}{3^2} + D)$ .

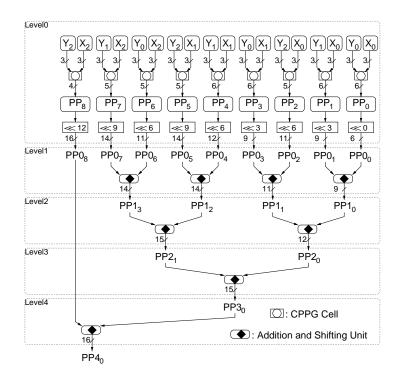

It should be emphasized again that all of the extra unnecessary hardware, due to the padded 0's to the operands or the padded 0 values additional partial products, is trimmed out, by the CAD tool, in the final design. The final design after the tool trims out the unnecessary hardware is shown in Figure 3

We follow the same previous techniques for designing binary multipliers using  $4 \times 4$ ,  $5 \times 5$  and  $6 \times 6$  CPPG cells<sup>1</sup>.

The aforementioned technique is generalized in Algorithm 1 for any CPPG cell size  $r \times r$  and arbitrary operands sizes n and m.

<sup>&</sup>lt;sup>1</sup> The VHDL code for each of the CPPG cells is posted at [Al-Nounou, 2022] for the community.

Algorithm 1 Using  $r \times r$  CPPG cell to design  $n \times m$  Multiplier. **Input:** Operand A, Operand B, n: size of A, m: size of B, r: size of CPPG cell **Output:**  $C = A \times B$ **Require:** n, m multiple of r, otherwise, zeros padded to the left of the number 1: if  $A = A_{n-1}A_{n-2}A_{n-3}A_{n-4}\dots A_3A_2A_1A_0$  then  $A = 2^{n-r} A_{n-1} A_{n-2} A_{n-3} \dots A_{n-r+2} A_{n-r+1} A_{n-r}$ 2:  $+2^{n-2r}A_{n-r-1}A_{n-r-2}A_{n-r-3}\dots A_{n-2r+2}A_{n-2r+1}A_{n-2r}$  $+\dots+2^{2r}A_{3r-1}A_{3r-2}A_{3r-3}\dots A_{2r+2}A_{2r+1}A_{2r}$  $+2^{r}A_{2r-1}A_{2r-2}A_{2r-3}\ldots A_{r+2}A_{r+1}A_{r}$  $+2^{0}A_{r-1}A_{r-2}A_{r-3}\ldots A_{2}A_{1}A_{0}$ 3: end if 4: if  $B = B_{m-1}B_{m-2}B_{m-3}A_{m-4}\dots B_3A_2B_1B_0$  then  $B = 2^{m-r} B_{m-1} B_{m-2} B_{m-3} \dots B_{m-r+2} B_{m-r+1} B_{m-r}$ 5:  $+2^{m-2r}B_{m-r-1}B_{m-r-2}B_{m-r-3}\dots B_{m-2r+2}B_{m-2r+1}B_{m-2r}$  $+\cdots+2^{2r}B_{3r-1}B_{3r-2}B_{3r-3}\ldots B_{2r+2}B_{2r+1}B_{2r}$  $+2^{r}B_{2r-1}B_{2r-2}B_{2r-3}\dots B_{r+2}B_{r+1}B_{r}$  $+2^{0}B_{r-1}B_{r-2}B_{r-3}\ldots B_{2}B_{1}B_{0}$ 6: end if 7: for  $s = 1, 2, 3, \dots, \frac{n}{r} - 2, \frac{n}{r} - 1, \frac{n}{r}$  do k = n - rs8:  $X_{\underline{k}} = A_{k+r-1}A_{k+r-2}A_{k+r-3}\dots A_{k+2}A_{k+1}A_k$ 9:  $A = \sum_{i=0}^{r} 2^{ri} X_i$ 10: 11: end for 12: for  $s = 1, 2, 3, \ldots, \frac{m}{r} - 2, \frac{m}{r} - 1, \frac{m}{r}$  do k = m - rs13:  $Y_{\frac{k}{r}} = B_{k+r-1}B_{k+r-2}B_{k+r-3}\dots B_{k+1}B_{k+1}B_k$ 14:  $B^{r} = \sum_{j=0}^{\frac{m}{r}-1} 2^{rj} Y_{j}$ 15: 16: end for 17:  $D = 2^{\lceil (\log_2 \frac{mn}{r^2}) \rceil} - \frac{mn}{r^2}$ 11. D = 218: for i = 0 to  $\frac{n}{r} - 1$  do 19: for j = 0 to  $\frac{m}{r} - 1$  do 20:  $PP_{\frac{ni}{r}+j} = X_i Y_j$ 21:  $PP_{\frac{n}{2}i+j}^0 = 2^{2(i+j)} PP_{\frac{n}{2}i+j}$ 22: end for 23: end for 24: Pad D additional partial products of 0 values to the shifted partial products. 24: Pad *D* additional particular 25:  $L = \log_2(\frac{mn}{r^2} + D)$ 26: for l = 1 to *L* do 27: for t = 0 to  $(\frac{mn}{r^2} + D)/2^l - 1$  do 28:  $PP_t^l = (PP_{(2t+1)}^{l-1} + PP_{2t}^{l-1})$ end for 29. 30: end for 31:  $C = PP_0^L((m+n) - 1 \quad downto \quad 0)$

*Figure 2: The structure of an*  $8 \times 8$  *multiplier using the*  $3 \times 3$  *CPPG cell.*

# 4 Results and discussions

The proposed CPPG cell presented in Section 3 are used to design  $8 \times 8$ ,  $16 \times 16$ ,  $32 \times 32$ ,  $64 \times 64$ , and  $128 \times 128$  binary multipliers. All of the proposed CPPG cells and the designed binary multipliers are described and functionally verified using VHDL and Xilinx ISE 14.6 simulation tools. In addition, the proposed CPPG cells and the designed

Figure 3: The structure of an  $8 \times 8$  multiplier using the  $3 \times 3$  CPPG cell after the tool trims out unnecessary hardware.

binary multipliers are synthesized and implemented using Xilinx ISE 14.6 synthesis and implementation tools. Different FPGA families and devices are targeted.

#### 4.1 Implementation of the proposed CPPG cells

The proposed CPPG cells are implemented using different FPGA families. The implementation results are listed in Table 1. As expected, the area and delay increase with the size of the cell. Generally, the best delay is achieved when the Virtex-7 FPGA family is targeted. The delay results are reported after the synthesis process of the tool. The implementation results for the  $128 \times 128$  and  $64 \times 64$  binary multipliers using the different CPPG cells targeting the Virtex-7 FPGA family are listed in Table 2. While, those for the  $32 \times 32$  and  $16 \times 16$  binary multipliers are listed in Table 3.

It can be observed that, for all investigated multipliers, the best area is achieved when utilizing the  $3 \times 3$  CPPG cell. While, the best delay for the  $128 \times 128$ , the  $64 \times 64$ , and the  $32 \times 32$  multipliers is achieved when utilizing the  $4 \times 4$  CPPG cell. For the  $16 \times 16$  multiplier, the best delay is achieved when utilizing the  $5 \times 5$  CPPG cell. The second best area for the  $128 \times 128$  and the  $64 \times 64$  multipliers is achieved with the  $4 \times 4$  CPPG cell. While the second best area for the  $32 \times 32$  and the  $16 \times 16$  multipliers is achieved with the  $2 \times 2$  CPPG cell. The second best delay for the  $128 \times 128$ , the  $64 \times 64$ , and the  $32 \times 32$  multipliers is achieved when utilizing the  $2 \times 2$  CPPG cell. The second best delay for the  $128 \times 128$ , the  $64 \times 64$ , and the  $32 \times 32$  multipliers is achieved when utilizing the  $2 \times 2$  CPPG cell. The second best delay for the  $128 \times 128$ , the  $64 \times 64$ , and the  $32 \times 32$  multipliers is achieved when utilizing the  $2 \times 2$  CPPG cell. On the other hand, the second best delay for the  $16 \times 16$  multiplier is achieved with the  $4 \times 4$  CPPG cell. Utilizing the  $6 \times 6$

| FPGA     | Metric            | CPPG cell size                                         |       |       |       |       |  |  |

|----------|-------------------|--------------------------------------------------------|-------|-------|-------|-------|--|--|

| ITUA     | wieure            | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |       |       |       |       |  |  |

|          | Area (Slice LUTs) | 4                                                      | 6     | 32    | 199   | 785   |  |  |

| Virtex-5 | Area (Slices)     | 2                                                      | 2     | 11    | 74    | 344   |  |  |

|          | Delay (ns)        | 3.885                                                  | 4.129 | 5.595 | 6.996 | 9.778 |  |  |

|          | Area (Slice LUTs) | 2                                                      | 5     | 39    | 134   | 463   |  |  |

| Virtex-6 | Area (Slices)     | 1                                                      | 2     | 19    | 54    | 156   |  |  |

|          | Delay (ns)        | 0.989                                                  | 1.13  | 2.953 | 3.57  | 4.913 |  |  |

| Virtex-7 | Area (Slice LUTs) | 2                                                      | 5     | 39    | 135   | 458   |  |  |

|          | Area (Slices)     | 1                                                      | 3     | 21    | 54    | 154   |  |  |

|          | Delay (ns)        | 0.921                                                  | 1.023 | 2.595 | 3.217 | 4.73  |  |  |

Table 1: Implementation results for the proposed CPPG cells over different FPGA families

|      | 128×128 |          |        |        | 64×64    |        |

|------|---------|----------|--------|--------|----------|--------|

| CPPG | Area    | Area     | Delay  | Area   | Area     | Delay  |

| cell | (LUTs)  | (Slices) | (ns)   | (LUTs) | (Slices) | (ns)   |

| 2×2  | 137947  | 39278    | 15.388 | 19457  | 6113     | 11.952 |

| 3×3  | 71356   | 20031    | 16.608 | 12126  | 4214     | 12.448 |

| 4×4  | 80293   | 28733    | 15.081 | 16247  | 5674     | 11.673 |

| 5×5  | 114471  | 39157    | 17     | 20616  | 7265     | 13.325 |

| 6×6  | 235362  | 74207    | 15.853 | 42178  | 15181    | 12.985 |

*Table 2: Implementation results for the 128×128 and 64×64 binary multipliers using the proposed CPPG cells and targeting the Virtex-7 FPGA family.*

|           |        | 32×32    |        |        | 16×16    |       |

|-----------|--------|----------|--------|--------|----------|-------|

| CPPG cell | Area   | Area     | Delay  | Area   | Area     | Delay |

| CPPG cell | (LUTs) | (Slices) | (ns)   | (LUTs) | (Slices) | (ns)  |

| 2×2       | 3135   | 1044     | 9.232  | 675    | 314      | 7.056 |

| 3×3       | 2267   | 808      | 9.475  | 508    | 243      | 7.821 |

| 4×4       | 3567   | 1184     | 8.865  | 807    | 364      | 7.023 |

| 5×5       | 4762   | 1673     | 9.456  | 1172   | 419      | 6.82  |

| 6×6       | 10249  | 3557     | 10.089 | 2300   | 716      | 7.304 |

Table 3: Implementation results for the  $32 \times 32$  and  $16 \times 16$  binary multipliers using the proposed CPPG cells and targeting the Virtex-7 FPGA family.

CPPG cell reduces the number of partial products and the complexity of the addition phase. Theoretically, this would result in better performance. Unexpectedly, the implementation results show that the worst performance is achieved whenever the  $6 \times 6$  CPPG cell is used. The huge complexity of the Boolean equations of the  $6 \times 6$  CPPG cell can be a justification for this drawback in performance. It happens that the  $3 \times 3$  CPPG cell provides an acceptable reduction in the number of partial products while maintaining low hardware complexity.

#### 4.2 Comparisons with works in literature

The proposed binary multipliers in this work are compared with different works presented in the literature. For a fair comparison, the size of the proposed binary multipliers is chosen to be equal to the size of the binary multipliers presented in the literature. In addition, the implementation environment is chosen to be the same as that used in the work from the literature. That is, the FPGA family used to implement the proposed binary multiplier is chosen to be the same FPGA family that is used to implement the binary multipliers presented in the literature. Each work from the literature that is to be used for the comparison purpose is represented with a symbol according to Table 4.

| Symbol | Work                              |

|--------|-----------------------------------|

| $W_a$  | [Akhter and Chaturvedi, 2019]     |

| $W_b$  | [Sharma, 2015]                    |

| $W_c$  | [Mani et al., 2015]               |

| $W_d$  | [Atre and Alshewimy, 2017]        |

| $W_e$  | [Chaudhary and Kularia, 2016]     |

| $W_f$  | [Bais and khan Ali, 2016]         |

| $W_g$  | [Solanki et al., 2021]            |

| $W_h$  | [Chandrashekara and Rohith, 2019] |

| $W_i$  | [Van Toan and Lee, 2020]          |

| $W_j$  | [Naqvi, 2017]                     |

| $W_k$  | [Jais and Palsodkar, 2016]        |

| $W_l$  | [Wallace, 1964]                   |

| $W_m$  | [Waters and Swartzlander, 2010]   |

| $W_n$  | [Asif and Kong, 2015a]            |

| $W_o$  | [Asif and Kong, 2015b]            |

| $W_p$  | [Saha et al., 2018]               |

| $W_q$  | [Fritz and Fam, 2017]             |

| $W_r$  | [Murugeswari and Mohideen, 2014]  |

Table 4: Symbols that are used to represent some works from the literature.

Table 5 lists the comparison results for operand sizes of 4 and 8. While, Table 6 lists the comparison results for operand sizes of 16, 32, 64, and 128. The results reported for our designs are based on utilizing the  $2 \times 2$  CPPG cell. In these two tables, if a result is not reported for a reference then we use *'not reported'* (NR) in the corresponding cell. Generally, the proposed multipliers outperform those presented in the literature in terms of delay with an area penalty in some cases.

Based on Tables 5 and 6, the proposed  $16 \times 16$  multiplier, over Virtex-4 FPGA, achieves 21.8% reduction in delay and 47.9% reduction in area comparing to its counterpart in [Atre and Alshewimy, 2017]. It is also clear that over Spartan-3E FPGA, it beats the  $16 \times 16$  multiplier of [Solanki et al., 2021] in terms of delay with 18% extra area penalty. The authors in [Solanki et al., 2021] mention that the minimum periods in their  $8 \times 8$  and  $16 \times 16$  multipliers are 9.29 and 10.27 *ns*, respectively. The cycles needed to output the product are 16 and 32 cycles, respectively. Hence, the delay of their

| (ns)           8.54           7.557           15.42           13.382           18.534           17.864           12.738           10.43           8.568           11.109           8.437           4.706 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.557<br>15.42<br>13.382<br>18.534<br>17.864<br>12.738<br>10.43<br>8.568<br>11.109<br>8.437<br>4.706                                                                                                     |

| 15.42           13.382           18.534           17.864           12.738           10.43           8.568           11.109           8.437           4.706                                               |

| 13.382           18.534           17.864           12.738           10.43           8.568           11.109           8.437           4.706                                                               |

| 18.534           17.864           12.738           10.43           8.568           11.109           8.437           4.706                                                                                |

| 17.864<br>12.738<br>10.43<br>8.568<br>11.109<br>8.437<br>4.706                                                                                                                                           |

| 12.738<br>10.43<br>8.568<br>11.109<br>8.437<br>4.706                                                                                                                                                     |

| 10.43           8.568           11.109           8.437           4.706                                                                                                                                   |

| 8.568<br>11.109<br>8.437<br>4.706                                                                                                                                                                        |

| 11.109<br>8.437<br>4.706                                                                                                                                                                                 |

| 8.437<br>4.706                                                                                                                                                                                           |

| 4.706                                                                                                                                                                                                    |

|                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |

| 15.37                                                                                                                                                                                                    |

| 13.87                                                                                                                                                                                                    |

| 12.247                                                                                                                                                                                                   |

| 28.73                                                                                                                                                                                                    |

| 28.669                                                                                                                                                                                                   |

| 28.601                                                                                                                                                                                                   |

| 20.694                                                                                                                                                                                                   |

| 148.64                                                                                                                                                                                                   |

| 34.629                                                                                                                                                                                                   |

| 30.75                                                                                                                                                                                                    |

| 16.595                                                                                                                                                                                                   |

| 18.46                                                                                                                                                                                                    |

| 25.86                                                                                                                                                                                                    |

| 23.106                                                                                                                                                                                                   |

| 16.478                                                                                                                                                                                                   |

| 14.219                                                                                                                                                                                                   |

| 5.15                                                                                                                                                                                                     |

| 6.25                                                                                                                                                                                                     |

| 11.208                                                                                                                                                                                                   |

| 26.501                                                                                                                                                                                                   |

| 11.314                                                                                                                                                                                                   |

| 6.281                                                                                                                                                                                                    |

|                                                                                                                                                                                                          |

Table 5: Comparisons with different works presented in literature for operand sizes of4 and 8.

designs is computed as  $(16 \times 9.29 = 148.64ns$  for the  $8 \times 8$  multiplier) and  $(32 \times 10.27 = 328.64ns$  for the  $16 \times 16$  multiplier). In fact, their major concern is low-power design.

The proposed multipliers in [Van Toan and Lee, 2020] are approximate multipliers that do not provide exact results as produced by the proposed multipliers in this work. These approximate multipliers can be used in applications where exact results are not

| Operand | Work              | FPGA           | Area     | Area    | Delay    |

|---------|-------------------|----------------|----------|---------|----------|

| size    | WOIK              | ГРОА           | (Slices) | (LUT's) | (ns)     |

|         | $W_d$ (Radix-32)  | N.C            | 726      | NR      | 20.35    |

|         | Proposed          | Virtex-4       | 378      | 667     | 15.913   |

| 16      | $W_f$ (WT)        | Successfully 2 | 444      | 819     | 51.090   |

| 16      | Proposed          | Spartan-3      | 373      | 672     | 32.174   |

|         | $W_q$             | Constant 2E    | NR       | 473     | 328.64   |

|         | Proposed          | Spartan-3E     | 377      | 578     | 22.234   |

|         | $W_i$ (LUT-Based) |                | NR       | 923     | 7.46     |

|         | $W_i$ (DSP-Based) | Spartan-6      | NR       | 372     | 6.40     |

|         | Proposed          | _              | 323      | 673     | 17.26    |

|         | $W_d$ (Radix-32)  | Virtex-4       | 2400     | NR      | 27.95    |

| 32      | Proposed          | Villex-4       | 1877     | 3135    | 20.242   |

| 52      | $W_f$ (WT)        | Sporton 2      | 2021     | 3765    | 88.114   |

|         | Proposed          | – Spartan-3    | 1593     | 2896    | 41.397   |

|         | $W_i$ (LUT-Based) |                | NR       | 3499    | 11.30    |

|         | $W_i$ (DSP-Based) | Spartan-6      | NR       | 1496    | 18.04    |

|         | Proposed          |                | 1179     | 3152    | 21.31    |

|         | $W_d$ (Radix-32)  |                | 8770     | NR      | 46.11    |

|         | $W_e$ (Array)     |                | 4653     | 9110    | 1525.592 |

|         | $W_e$ (Booth)     | Virtex-4       | 8097     | 16192   | 138.25   |

|         | $W_e$ (Vedic)     |                | 1817     | 2289    | 29.967   |

|         | Proposed          |                | 8458     | 13773   | 24.442   |

|         | $W_j$             |                | NR       | 8185    | 21.243   |

| 64      | $W_k$             | Virtex-5       | NR       | 2622    | 21.985   |

|         | Proposed          |                | 4305     | 11210   | 17.176   |

|         | $W_k$             |                | NR       | 2622    | 15.77    |

|         | $W_j$             | Virtex-6       | NR       | 8185    | 12.717   |

|         | Proposed          |                | 5944     | 19482   | 12.137   |

|         | $W_k$             | Spartan-6      | NR       | 2622    | 24.932   |

|         | Proposed          | Spartan-0      | 6627     | 19551   | 22.328   |

| 128     | $W_d$ (Radix-32)  | Virtex-4       | 31960    | NR      | 59.98    |

| 120     | Proposed          | VIIICA-4       | 44517    | 63724   | 32.184   |

1048 Al-Nounou A.A., Al-Khaleel O., Obeidat F., Al-Khaleel M.: FPGA Implementation ...

*Table 6: Comparisons with different works presented in literature for operand sizes of 16, 32, 64, and 128.*

mandatory for the application to produce the expected output. However, the authors use the core generator of the Xilinx Tools to generate two IP cores for comparison purposes. The first one is a LUT-Based exact multiplier and the second one is a DSP-Based exact multiplier.

For the LUT-Based core, the area is reported in terms of the number of LUTs and the number of CARRY4 embedded components, which consists of four  $2 \times 1$ -MUXs and four XOR gates. Therefore, the area of each CARRY4 embedded component can be estimated to be 8 LUTs. As a result, the area of the LUT-Based core is the number

of the reported LUTs plus the number of reported CARRY4 components multiplied by 8. For example, for the  $16 \times 16$  LUT-Based multiplier, the authors reported that the area is (299 LUTs + 78 CARRY4). This means that the estimated area in LUTs is (299 +  $78 \times 8 = 923$  LUTs).

For the DSP-Based core, the area is reported in terms of the number of LUTs and the number of utilized DSP embedded components. The DSPs in Xilinx FPGAs are known to be  $18 \times 18$  in size. The estimated area of a DSP component in terms of LUTs can be easily extracted from the Core Generator tool itself. It is founded that the area for an  $18 \times 18$  DSP core is 364 LUTs. As a result, the area of the DSP-Based core is the number of the reported LUTs plus the number of the reported DSP components multiplied by 364. For example, for the  $16 \times 16$  LUT-Based multiplier, the authors reported that the area is (8 LUTs + 1 DSP). This means that the estimated area in LUTs is  $(8 + 1 \times 364 = 372 LUTs)$ .

From Tables 5 and 6, it is clear that the proposed multipliers in this work achieves smaller area comparing to the LUT-Based  $8 \times 8$ , the  $16 \times 16$ , and the  $32 \times 32$  multipliers presented in [Van Toan and Lee, 2020]. The proposed 8 × 8 multiplier is smaller in area than the  $8 \times 8$  DSP-Based multiplier of [Van Toan and Lee, 2020]. While, the  $16 \times 16$ , and the  $32 \times 32$  DSP-Based multipliers of [Van Toan and Lee, 2020] are smaller than the proposed ones. When it comes to the delay, it looks that the multipliers of [Van Toan and Lee, 2020] are faster for all operand sizes. However, while investigating the area of the  $18 \times 18$  DSP, we noticed that the authors in [Van Toan and Lee, 2020] have reported the delay of their designs after registering the inputs and the output. This means that their delay is the minimum period of the design and it is not a combinational path delay that involves the delay of the IO buffers as in our case. The IO buffers delay is the routing delay from the FPGA pins to the ports of the design. This delay varies according to where the tool places the design inside the FPGA. When registering the inputs and the output of our  $8 \times 8$  multiplier, we get a minimum period of 7.877ns over Spartan-6 FPGA. Also, if we exclude the IO buffer delay, then the delays of our combinational  $8 \times 8$ ,  $16 \times 16$ , and the  $32 \times 32$  multipliers over Spartan-6 FPGA become 6.94 ns, 10.89 ns, and 14.52 ns, respectively. Moreover, Two points should be raised here. The first one is that the multipliers of [Van Toan and Lee, 2020] are generated IP cores that are part of the CAD tool itself and these IP cores can be generated for operand size of up to a maximum  $64 \times 64$  and not more than that, which limits the scalability of the multiplication in [Van Toan and Lee, 2020]. While the proposed approach in this work is scalable and is not limited to any operand size. The second point is that using these embedded IP cores limits the portability of the HDL code to Xilinx FPGA platforms. While in the proposed approach, the HDL can be implemented in any FPGA or ASIC platform.

Over Spartan-3E FPGA and comparing to the  $4 \times 4$  Wallace Tree (WT) and Dadda multipliers of [Sharma, 2015], the proposed multiplier achieves 31.2% and 28.69% improvement in speed, respectively. The area is also reduced by 31.8% and 34.7%, respectively. For the size of  $8 \times 8$  over Spartan-3E FPGA, the proposed multiplier also shows better results in terms of area and speed compared to those WT and Dadda multipliers of [Sharma, 2015]. In fact, there is 35.3% and 39.5% reduction in the area with 52% and 46% reduction in delay, respectively.

Furthermore, the proposed  $8 \times 8$  multiplier over Spartan-6 FPGA achieves 56.6%, 51.4%, and 31.9% improvement in speed compared to the Booth, Array, and WT multipliers of [Chandrashekara and Rohith, 2019], respectively. In this case, the area of the proposed multiplier is reduced by 43.5% compared to the Booth multipliers and slightly reduced compared to the Array and WT multipliers.

The proposed  $8 \times 8$  multiplier, over Artix-7 FPGA, achieves 44.4% reduction in delay with only 11.1% increase in the area compared to the Improved Wallace Tree (IWT) multiplier of [Mani et al., 2015]

Over Spartan-3, the proposed  $16 \times 16$  multiplier outperforms its counterpart WT multiplier in [Bais and khan Ali, 2016] in terms of area and speed. It is 1.58 times faster and 1.19 times smaller. On the other hand, the proposed  $32 \times 32$  multiplier is 2.12 times faster and 1.26 smaller compared with the  $32 \times 32$  WT multiplier in [Bais and khan Ali, 2016].

The  $64 \times 64$  Booth and Array multipliers in [Chaudhary and Kularia, 2016] are also compared with the proposed multiplier over Virtex-4 FPGA. The results show that the proposed multipliers achieve much better speed with a considerable area penalty, especially in the case of the Array multiplier.

The proposed  $64 \times 64$  multiplier shows minor speed improvement over the multiplier in [Naqvi, 2017] when targeting Virtex-6 FPGA. However, over Virtex-5 FPGA, it shows 19.14% speed improvement with 26.98% extra area.

Targeting Virtex-4 FPGA, a 46.3% speed improvement is achieved by the proposed  $128 \times 128$  multiplier over the multiplier in [Atre and Alshewimy, 2017]. However, there is a 28.2% area penalty in this case.

The Area-Time product for the results in Tables 5 and 6 are calculated and listed in Tables 7 and 8. Although the proposed multipliers show improvement in speed compared to other similar works presented in the literature, one finds in some cases that the Area-Time product for the proposed multipliers is higher than its counterpart presented in the literature. This is due to the fact that in these cases, the proposed multiplier achieves better speed with a considerable extra area penalty.

#### 4.3 Power comparison

The proposed  $8 \times 8$  multiplier is implemented in Spartan-3E FPGA and compared, in terms of power, with other  $8 \times 8$  multipliers from literature. In order to get the power analysis from the tool, the proposed  $8 \times 8$  multiplier is implemented such that the inputs and the outputs are registered. The inputs are registered with 8-bit parallel in parallel out (PIPO) registers. The output is also registered with a PIPO register. However, the register at the output is 16-bit input and 8-bit output. This means that to get the final product out, two cycles are needed. The power results of the proposed multiplier and for other works from literature are listed in Table 9 where (CBWT) refers to Counter-Based Wallace Tree and (RCWT) refers to Reduced Complexity Wallace Tree. The results of other multipliers are taken from [Solanki et al., 2021].

The proposed  $8 \times 8$  multiplier outperforms all other multipliers in terms of power with an acceptable increase in clock cycle delay in some cases. For example, there is 25.39% reduction in power compared to [Solanki et al., 2021] with only 14.06% increase in clock cycle delay. It can be figured out that although the proposed  $8 \times 8$  multiplier shows a small improvement in power compared to [Wallace, 1964], it shows 20.65% reduction in area. In fact, the proposed  $8 \times 8$  multiplier outperforms all other multipliers, listed in Table 9, in terms of area.

#### 4.4 Utilizing the proposed multiplier in a MAC Unit

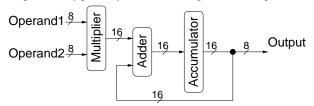

The Multiply-Accumulate (MAC) unit is a basic and essential digital component in most microprocessors and Digital Signal Processors (DSPs). The MAC unit is used to efficiently accelerate the computations of FIR or FFT/IFFT, which are required by dataintensive applications such as filters, orthogonal frequency-division multiplexing algorithms, and channel estimators[Hoang et al., 2010]. As shown by Figure 4, the main

| Operand | Work              | FPGA        | A×T         | A×T       |

|---------|-------------------|-------------|-------------|-----------|

| size    | WOIK              | ГРОА        | (Slices.ns) | (LUTs.ns) |

|         | $W_a$             | Vinton 4    | NA          | 256       |

|         | Proposed          | Virtex-4    | 325         | 635       |

|         | $W_a$             | Successor 2 | NA          | 463       |

|         | Proposed          | Spartan-3   | 562         | 1111      |

|         | $W_b$ (WT)        |             | 408         | 723       |

| 4       | $W_b$ (Dadda)     | Spartan-3E  | 411         | 697       |

| 4       | Proposed          |             | 191         | 344       |

|         | $W_a$             | Sporton 6   | NA          | 250       |

|         | Proposed          | Spartan-6   | 120         | 334       |

|         | $W_c$ (WT)        |             | NA          | 289       |

|         | $W_c$ (IWT)       | Artix-7     | NA          | 186       |

|         | Proposed          |             | NA          | 118       |

|         | $W_d$ (Radix-32)  |             | 3904        | NA        |

|         | $W_a$             | Virtex-4    | NA          | 2122      |

|         | Proposed          |             | 931         | 1678      |

|         | $W_a$             |             | NA          | 4396      |

|         | $W_e$             | Sucretary 2 | 3010        | 5504      |

|         | $W_f$ (WT)        | Spartan-3   | 2774        | 5177      |

|         | Proposed          |             | 1552        | 2835      |

|         | $W_g$             |             | NA          | 23931     |

|         | $W_b$ (WT)        | Sucreton 2E | 4017        | 7099      |

|         | $W_b$ (Dadda)     | Spartan-3E  | 3813        | 6704      |

| 0       | Proposed          |             | 1245        | 2108      |

| 8       | $W_a$             |             | NA          | 2308      |

|         | $W_h$ (Booth)     |             | NA          | 5586      |

|         | $W_h$ (Array)     |             | NA          | 3004      |

|         | $W_h$ (WT)        | Smorton (   | NA          | 2389      |

|         | $W_h$ (Vedic)     | Spartan-6   | NA          | 1820      |

|         | $W_i$ (LUT-Based) | 1           | NA          | 1051      |

|         | $W_i$ (DSP-Based) | 1           | NA          | 2319      |

|         | Proposed          | 1           | 639         | 1367      |

|         | $W_c$ (WT)        |             | NA          | 5433      |

|         | $W_c$ (IWT)       | Artix-7     | NA          | 1448      |

|         | Proposed          | 1           | NA          | 904       |

Table 7: Comparisons of Area-Time product with different works presented inliterature for operand sizes of 4 and 8.

components of a MAC unit are Multiplier, Adder, and Accumulator. The Efficiency of the multiplier highly affects the overall performance of the MAC. The proposed multiplier is utilized in designing an 8-bit MAC unit to demonstrate its efficiency. Once the MAC finishes computation, the result is output in 2 cycles (8 bits/cycle). A VHDL code description for the MAC unit is developed and the design is implemented target-

|         | 1                 |                | r           |           |

|---------|-------------------|----------------|-------------|-----------|

| Operand | Work              | FPGA           | A×T         | A×T       |

| size    |                   | ITUA           | (Slices.ns) | (LUTs.ns) |

|         | $W_d$ (Radix-32)  | Virtex-4       | 14774       | NA        |

|         | Proposed          | VIIICA-4       | 6015        | 10614     |

|         | $W_f$ (WT)        | Superton 2     | 22684       | 41843     |

|         | Proposed          | Spartan-3      | 12001       | 21621     |

| 16      | $W_g$             | Sporton 2E     | NA          | 155447    |

|         | Proposed          | Spartan-3E     | 8382        | 12851     |

|         | $W_i$ (LUT-Based) |                | NA          | 6886      |

|         | $W_i$ (DSP-Based) | Spartan-6      | NA          | 2381      |

|         | Proposed          |                | 5575        | 11616     |

|         | $W_d$ (Radix-32)  | Virtex-4       | 67080       | NA        |

|         | Proposed          | Virtex-4       | 37994       | 63459     |

|         | $W_f$ (WT)        | Successfully 2 | 178078      | 331749    |

| 32      | Proposed          | Spartan-3      | 65945       | 119886    |

|         | $W_i$ (LUT-Based) |                | NA          | 39539     |

|         | $W_i$ (DSP-Based) | Spartan-6      | NA          | 26988     |

|         | Proposed          |                | 25124       | 67169     |

|         | $W_d$ (Radix-32)  |                | 404385      | NA        |

|         | $W_e$ (Array)     |                | 7098580     | 13898143  |

|         | $W_e$ (Booth)     | Virtex-4       | 1119410     | 2238544   |

|         | $W_e$ (Vedic)     |                | 54450       | 68594     |

|         | Proposed          |                | 206730      | 336640    |

|         | $W_i$             |                | NA          | 173874    |

| 64      | $W_k$             | Virtex-5       | NA          | 57645     |

|         | Proposed          |                | 73943       | 192543    |

|         | $W_k$             |                | NA          | 41349     |

|         | $W_i$             | Virtex-6       | NA          | 104089    |

|         | Proposed          |                | 72142       | 236453    |

|         | $W_k$             | Sporton 6      | NA          | 65372     |

|         | Proposed          | Spartan-6      | 147968      | 436535    |

| 129     | $W_d$ (Radix-32)  | Virtar A       | 1916961     | NA        |

| 128     | Proposed          | Virtex-4       | 1432735     | 2050893   |

1052 Al-Nounou A.A., Al-Khaleel O., Obeidat F., Al-Khaleel M.: FPGA Implementation ...

Table 8: Comparisons of Area-Time product with different works presented in the literature for operand sizes of 16, 32, 64, and 128.

ing Spartan-3E FPGA. The implementation results are listed in Table 10 and compared against the results of different MAC units, which are based on different multiplier designs from the literature. The implementation results show that the MAC unit of this work outperforms the different MAC units in terms of area and power, and power-delay product. For example, the MAC with the proposed multiplier achieves 18.3% reduction in power, 32.2% reduction in area, and 36.3% improvement in power-delay product compared to the MAC in [Solanki et al., 2021]. Hence, the proposed multiplier improves the efficiency of the MAC unit.

| Al-Nounou A.A., Al-Khaleel O., Obeidat F., Al-Khaleel M.: FPGA Implementation | 1053 |

|-------------------------------------------------------------------------------|------|

|-------------------------------------------------------------------------------|------|

| Multiplier   | Power<br>(mW) | Dynamic<br>power<br>(mW) | Mini.<br>period<br>(ns) | Maxi.<br>Freq.<br>(MHz) | Area<br>(LUTs) | Power<br>delay<br>product<br>(pJ) |

|--------------|---------------|--------------------------|-------------------------|-------------------------|----------------|-----------------------------------|

| $W_l$ (WT)   | 70.93         | 37.06                    | 10.14                   | 98.57                   | 184            | 719.23                            |

| $W_m$ (RCWT) | 117.23        | 35.80                    | 11.87                   | 84.23                   | 184            | 1391.63                           |

| $W_n$ (CBWT) | 123.72        | 42.20                    | 12.70                   | 78.69                   | 190            | 1571.24                           |

| Wo           | 88.67         | 7.59                     | 9.57                    | 104.42                  | 164            | 848.57                            |

| $W_p$        | 88.35         | 7.28                     | 9.47                    | 105.52                  | 162            | 836.67                            |

| $W_q$        | 88.16         | 7.09                     | 11.83                   | 84.48                   | 169            | 1042.93                           |

| $W_r$        | 88.21         | 7.14                     | 9.53                    | 104.93                  | 165            | 840.64                            |

| $W_g$        | 87.12         | 6.06                     | 9.29                    | 107.55                  | 161            | 809.34                            |

| Proposed     | 65.00         | 3.10                     | 10.81                   | 92.52                   | 146            | 702.52                            |

*Table 9: Comparison of power for 8*  $\times$  8 *multipliers over Spartan-3E FPGA*.

| Multiplier  | Power<br>(mW) | Dynamic<br>power<br>(mw) | Minimum<br>period<br>(ns) | Area<br>(LUTs) | Power<br>delay<br>product<br>(pJ) |

|-------------|---------------|--------------------------|---------------------------|----------------|-----------------------------------|

| $W_l$ (WT)  | 126.72        | 45.16                    | 11.73                     | 236            | 1486.42                           |

| $W_m$ (RCW) | 126.55        | 45.00                    | 12.23                     | 240            | 1547.7                            |